# **FP-DAQ1616**

### FeaturePak<sup>™</sup> I/O Module with Analog Data Acquisition

Rev A3: May 2012

| Revision | Date      | Comment                                   |  |  |

|----------|-----------|-------------------------------------------|--|--|

| А        | 1/26/2011 | nitial version                            |  |  |

| A1       | 4/29/11   | D/A Waveform Generator information added  |  |  |

| A2       | 9/22/2011 | Specifications updated                    |  |  |

| A3       | 5/4/12    | Resolution information added, minor edits |  |  |

FOR TECHNICAL SUPPORT PLEASE CONTACT:

support@diamondsystems.com

© Copyright 2012 Diamond Systems Corporation 555 Ellis Street Mountain View, CA 94043 USA Tel 1-650-810-2500 Fax 1-650-810-2525 www.diamondsystems.com

# CONTENTS

|    |                | afe Handling Information                                            |    |

|----|----------------|---------------------------------------------------------------------|----|

|    |                | ction                                                               |    |

|    |                | cription                                                            |    |

|    |                |                                                                     |    |

|    |                | urePak Resources Used By FP-DAQ1616                                 |    |

|    |                | nal Overview                                                        |    |

|    |                | tional Block Diagram                                                |    |

|    |                | DAQ1616 Board Drawing<br>Stor Pinout and Pin Description            | o  |

|    |                | urePak Connector                                                    |    |

| 5. | 3.1.1          | PCI Express                                                         |    |

|    | 3.1.2          | System Interface Signals                                            |    |

| 3. |                | urePak Connector Pinout By Pin                                      |    |

| 3. |                | og I/O Signals                                                      |    |

| 3. |                | al I/O Signals                                                      |    |

|    |                | of Operation                                                        |    |

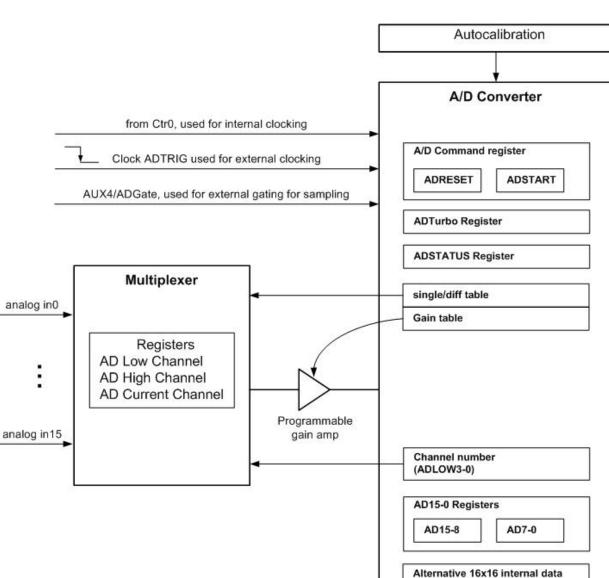

| 4. |                | Block                                                               |    |

| 4. |                | Block                                                               |    |

| 4. |                | Block                                                               |    |

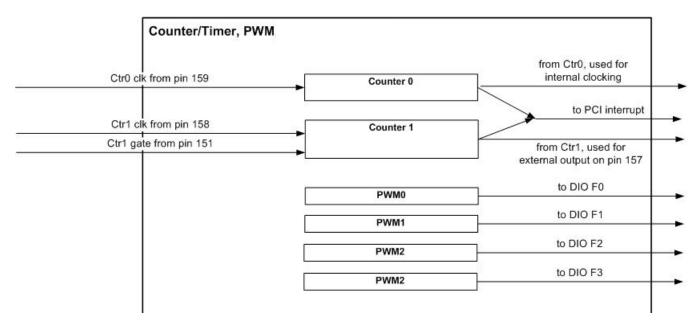

| 4. |                | nter Timer & PWM Block                                              |    |

| 4. |                | rupts                                                               |    |

| 4. |                | )                                                                   |    |

| 5. |                | Configuration                                                       |    |

| 5. |                | iguring Using Universal Driver                                      |    |

| 5. | 2 Conf         | iguring Using Register Operations                                   | 16 |

|    | 5.2.1          | Interrupt level                                                     |    |

|    | 5.2.2          | Single-Ended / Differential A/D Channels                            |    |

|    | 5.2.3          | D/A Configuration                                                   | 17 |

| 6. | I/O Reg        | isters                                                              | 18 |

| 6. | 1 I/O N        | /ap Summary                                                         | 18 |

| 6. | 2 I/O F        | Register Details                                                    | 19 |

|    | 6.2.1          | BAR0 + 0 (0x00) A/D Block Registers                                 | 19 |

|    | 6.2.2          | BAR0 + 16 (0x10) D/A Block Registers                                | 28 |

|    | 6.2.3          | BAR0 + 32 (0x20) DIO Block Registers                                |    |

|    | 6.2.4          | BAR0 + 48 (0x30) Counters & PWM Block Registers                     |    |

|    | 6.2.5          | BAR0 + 64 (0x40) FIFO Block Registers                               |    |

|    | 6.2.6          | BAR0 + 80 (0x50) EEPROM/Calibration Block Registers                 |    |

|    | 6.2.7          | BAR0 + 112 (0x70) Interrupts, Miscellaneous, and ID Block Registers |    |

|    | 6.2.8          | BAR0 + 224 (0xE0) SPI Flash Interface Block Registers               |    |

|    | 6.2.9          | BAR0 + 240 (0xF0) Capabilities/Page Control Block Registers         |    |

| 7. | -              | Input Ranges and Resolution                                         |    |

|    | 7.1.1          | Unipolar and Bipolar Inputs                                         |    |

|    | 7.1.2          | Input Ranges and Resolution                                         |    |

|    | 7.1.3          | A/D Conversion Formulas                                             |    |

| ~  | 7.1.4          | Correlation Between A/D Code and Input Voltage                      |    |

| 8. |                | ning an A/D Conversion                                              |    |

| 8. |                | A/D FIFO                                                            |    |

| 9. |                | npling Methods                                                      |    |

| 9. |                | pling Modes                                                         |    |

|    | 9.1.1          | FIFO Description                                                    |    |

|    | 9.1.2<br>9.1.3 | Scan Sampling                                                       |    |

| 10 |                | Sequential Sampling Perform A/D Conversions Using Interrupts        |    |

|    |                | Output Ranges and Resolution                                        |    |

|    |                | cription                                                            |    |

|    |                | blution                                                             |    |

| I  | 11.2 Rest      | Full-Scale Range Selection                                          |    |

| 12 |                | ting an Analog Output                                               |    |

|    |                | igure the Desired Output Range                                      |    |

|    |                | D/A Simultaneous Bit                                                |    |

###

| · ·                                                   |    |

|-------------------------------------------------------|----|

| 12.3 Send Command to Update D/A Value                 |    |

| 12.4 Monitor DABUSY Signal                            |    |

| 12.5 D/A Waveform Generator                           | 77 |

| 12.5.1 Description                                    | 77 |

| 12.5.2 Programming the D/A Waveform Generator         | 77 |

| 12.5.3 Reset D/A Waveform Pointer                     | 77 |

| 12.5.4 Store D/A Values into Buffer                   | 77 |

| 12.5.5 Setup D/A Waveform Settings                    | 78 |

| 12.5.6 Start D/A Waveform Generator                   |    |

| 13. AutoCalibration                                   | 79 |

| 13.1 How Autocalibration Works                        | 80 |

| 13.2 How to Perform Autocalibration With Software     | 80 |

| 14. Digital I/O Operation                             |    |

| 14.1 Digital I/O Configuration Register               |    |

| 14.2 Mode 0 Digital I/O                               |    |

| 14.3 Latched Mode Behavior and Interrupts on DIO      |    |

| 14.3.1 Auxiliary Digital I/O                          |    |

| 15. Counter/Timer Operation                           | 85 |

| 15.1 Counter/Timer Features and Configuration Options |    |

| 15.2 Counter/Timer Configuration                      | 85 |

| 15.3 Counter/Timer Access and Programming             |    |

| 15.3.1 Counter/Timer commands                         |    |

| 15.4 Timer interrupts                                 |    |

| 16. PWM Operation                                     |    |

| 17. Specifications                                    |    |

|                                                       |    |

# **IMPORTANT SAFE HANDLING INFORMATION**

### WARNING!

### **ESD-Sensitive Electronic Equipment**

Observe ESD-safe handling procedures when working with this product.

Always use this product in a properly grounded work area and wear appropriate ESD-preventive clothing and/or accessories.

Always store this product in ESD-protective packaging when not in use.

### Safe Handling Precautions

The FP-DAQ1616 board contains a high density connector with many connections to sensitive electronic components. This creates many opportunities for accidental damage during handling, installation and connection to other equipment. The list here describes common causes of failure found on boards returned to Diamond Systems for repair. This information is provided as a source of advice to help you prevent damaging your Diamond (or any vendor's) embedded computer boards.

**ESD damage** – This type of damage is usually almost impossible to detect, because there is no visual sign of failure or damage. The symptom is that the board eventually simply stops working, because some component becomes defective. Usually the failure can be identified and the chip can be replaced. To prevent ESD damage, always follow proper ESD-prevention practices when handling computer boards.

**Damage during handling or storage** – On some boards we have noticed physical damage from mishandling. A common observation is that a screwdriver slipped while installing the board, causing a gouge in the PCB surface and cutting signal traces or damaging components.

Another common observation is damaged board corners, indicating the board was dropped. This may or may not cause damage to the circuitry, depending on what is near the corner. Most of our boards are designed with at least 25 mils clearance between the board edge and any component pad, and ground / power planes are at least 20 mils from the edge to avoid possible shorting from this type of damage. However these design rules are not sufficient to prevent damage in all situations.

A third cause of failure is when a metal screwdriver tip slips, or a screw drops onto the board while it is powered on, causing a short between a power pin and a signal pin on a component. This can cause overvoltage / power supply problems described below. To avoid this type of failure, only perform assembly operations when the system is powered off.

Sometimes boards are stored in racks with slots that grip the edge of the board. This is a common practice for board manufacturers. However our boards are generally very dense, and if the board has components very close to the board edge, they can be damaged or even knocked off the board when the board tilts back in the rack. Diamond recommends that all our boards be stored only in individual ESD-safe packaging. If multiple boards are stored together, they should be contained in bins with dividers between boards. Do not pile boards on top of each other or cram too many boards into a small location. This can cause damage to connector pins or fragile components.

**Power supply wired backwards** – Our power supplies and boards are not designed to withstand a reverse power supply connection. This will destroy each IC that is connected to the power supply (i.e. almost all ICs). In this case the board will most likely will be unrepairable and must be replaced. A chip destroyed by reverse power or by excessive power will often have a visible hole on the top or show some deformation on the top surface due to vaporization inside the package. **Check twice before applying power!**

**Overvoltage on analog input** – If a voltage applied to an analog input exceeds the design specification of the board, the input multiplexor and/or parts behind it can be damaged. Most of our boards will withstand an erroneous connection of up to  $\pm 35V$  on the analog inputs, even when the board is powered off, but not all boards, and not in all conditions.

**Overvoltage on analog output** – If an analog output is accidentally connected to another output signal or a power supply voltage, the output can be damaged. On most of our boards, a short circuit to ground on an analog output will not cause trouble.

**Overvoltage on digital I/O line** – If a digital I/O signal is connected to a voltage above the maximum specified voltage, the digital circuitry can be damaged. On most of our boards the acceptable range of voltages connected to digital I/O signals is 0-5V, and they can withstand about 0.5V beyond that (-0.5 to 5.5V) before being damaged. However logic signals at 12V and even 24V are common, and if one of these is connected to a 5V logic chip, the chip will be damaged, and the damage could even extend past that chip to others in the circuit

# 1. INTRODUCTION

### 1.1 Description

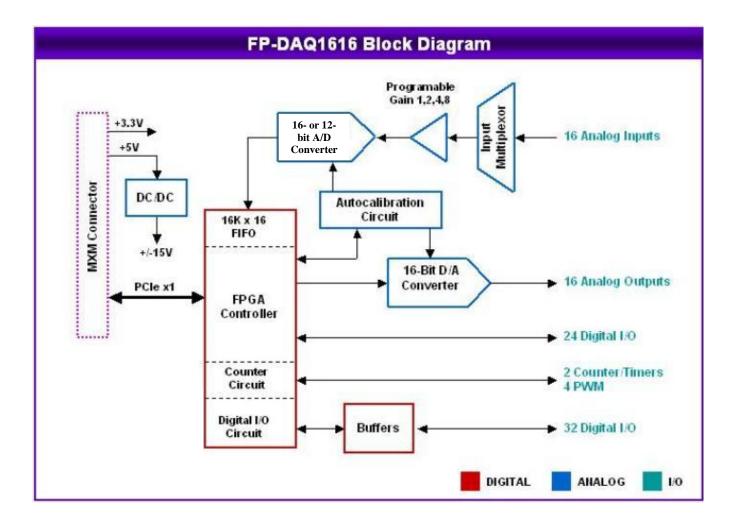

The FP-DAQ1616 is a FeaturePak-format data acquisition board with a full set of analog and digital I/O features.

It offers 16 single-ended or 8 differential analog voltage inputs with 12-bit resolution and programmable input range; 2.0MHz maximum aggregate A/D sampling rate with 16K FIFO operation; 16 analog voltage outputs with 16-bit resolution, user-selectable analog output ranges; 56 total programmable digital I/O bits, 3.3V logic compatible; one 32-bit counter/timer for A/D sampling rate control and one 32-bit counter/timer for user counting and timing functions; and four 24-bit PWM generators.

The FP-DAQ1616 has a PCI Express host interface brought out through the FeaturePak connector. All analog and digital I/O connects through this connector.

### 1.2 Features

#### **Analog Inputs**

16 12-bit or 16-bit analog inputs with up to 2MHz aggregate maximum sampling rate; 1MHz for multi-channel sampling

Programmable input ranges, polarity, and mode

16K sample A/D FIFO with programmable threshold

Autocalibration circuit with precision reference voltages

#### **Analog Outputs**

16 16-bit analog outputs with programmable range and polarity

D/A waveform generator

#### **Digital I/O**

56 programmable digital I/O

#### Counter/Timers and A/D Triggering

2 32-bit counter/timers for A/D timing and general purpose use

4 24-bit pulse-width modulator circuits

#### Miscellaneous

One PCI Express x1 lane host interface

FeaturePak form-factor compliant

Zero height expansion module

-40°C to +85°C operating temperature

Universal Driver software support

### 1.3 FeaturePak Resources Used By FP-DAQ1616

The following table identifies which resources among those defined by the FeaturePak specification that are used in this product:

| Company: Diamond   | d Systems Corp.                                                                                                |

|--------------------|----------------------------------------------------------------------------------------------------------------|

| Product: FP-DAQ16  | the second s |

| Host Interface Res | ources Supported                                                                                               |

| PCle x1 links      | 1                                                                                                              |

| USB channels       | -                                                                                                              |

| Serial port        | <u>52</u>                                                                                                      |

| SMBus              | 5                                                                                                              |

| PCIe Reset         | V                                                                                                              |

| Sys Reset          | V                                                                                                              |

| JTAG               | V                                                                                                              |

| +3.3V              | V                                                                                                              |

| +5V                | V                                                                                                              |

| +12V               | =                                                                                                              |

# 2. FUNCTIONAL OVERVIEW

### 2.1 Functional Block Diagram

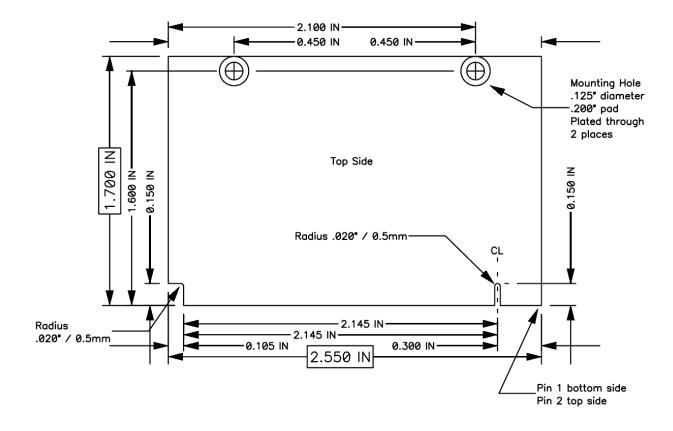

### 2.2 FP-DAQ1616 Board Drawing

# 3. CONNECTOR PINOUT AND PIN DESCRIPTION

### 3.1 FeaturePak Connector

The FP-DAQ1616 uses the FeaturePak standard, which provides a card form-factor and connector suitable for high-density, compact applications. See <u>http://featurepak.org/</u> for further details of the FeaturePak embedded I/O modules standard, including the specification.

In this document we will use the terms FeaturePak edge card connector and MXM connector interchangeably.

The FP-DAQ1616 uses an MXM 230-pin connector for all I/O, both to the main CPU for user I/O connections. The board contains gold-plated fingers conforming to the MXM physical standard for interfacing to the MXM connector.

The system interface signals on the MXM connector are predefined for all FeaturePak modules and a portion of pins are reserved for individual module I/O and are freely assignable for each module. Signals are grouped into several categories:

- System interface (PCIe)

- Slot/card management signals

- Dedicated user I/O

- Power/ground

- Reserved for future expansion

The module connects to 5 reserved pins to provide compatibility with possible future expansion of the FeaturePak standard.

The user I/O consists of 100 signals organized as 2 50-pin groups. On a general purpose baseboard, these signals directly drive 2 50-pin I/O connectors. The 50-pin connectors may then be connected to application-specific cabling, or an I/O adapter board may be plugged onto them to provide a custom I/O connector configuration for the system enclosure. A custom or application-specific main board may elect to use these signals in any way desired without conflicting with the standard.

A special feature of the FeaturePak I/O pin assignment is the electrical isolation provided on 32 of the module I/O pins on the primary 50-pin connector. These pins are separated from each other and from other connector pins by 34 unassigned pins (marked NC) which are to be left unconnected on the main board (<u>no pads or traces leading</u> to these pins). The module should omit the corresponding fingers on the edge connector.

#### 3.1.1 PCI Express

The FP-DAQ1616 uses a single PCI Express x1 link for its host interface and does not use the USB or serial interfaces allowed in the FeaturePak specification. It is reset by the PCI-Reset- input. The module routes the Slot ID signals to a register for readback by the host, and it drives the Present- output line low.

#### 3.1.2 System Interface Signals

Note: not all functionalities that are defined in the FeaturePak socket standard are supported by the FP-DAQ1616 module. For example, the USB and serial port interfaces are not utilized on this card.

### 3.2 FeaturePak Connector Pinout By Pin

This section indicates standard FeaturePak connector signal assignments. The I/OA and I/OB pin groups are mapped to specific I/O functions implemented by the FP-DAQ1616 board, as indicated in following sections.

|             | Pins 1 | – 114 |             |

|-------------|--------|-------|-------------|

| +3.3V       | 1      | 2     | +12V        |

| +3.3V       | 3      | 4     | PS-Current  |

| Ground      | 5      | 6     | Ground      |

| PCIe-TX1+   | 7      | 8     | PCIe-RX1+   |

| PCle-TX1-   | 9      | 10    | PCIe-RX1-   |

| Ground      | 11     | 12    | Ground      |

| PCIe-CLK1+  | 13     | 14    | PCIe-CLK2+  |

| PCIe-CLK1-  | 15     | 16    | PCIe-CLK2-  |

| Ground      | 17     | 18    | Ground      |

| PCIe-TX2+   | 19     | 20    | PCIe-RX2+   |

| PCIe-TX2-   | 21     | 22    | PCIe-RX2-   |

| Ground      | 23     | 24    | Ground      |

| PCIe-Reset- | 25     | 26    | Reserved    |

| Reserved    | 27     | 28    | Reserved    |

| Reserved    | 29     | 30    | Reserved    |

| Reserved    | 31     | 32    | Reserved    |

| Reserved    | 33     | 34    | Reserved    |

| Ground      | 35     | 36    | Ground      |

| USB-Ch1+    | 37     | 38    | USB-Ch2+    |

| USB-Ch1-    | 39     | 40    | USB-Ch2-    |

| Ground      | 41     | 42    | Ground      |

| +3.3V       | 43     | 44    | USB-OC1/2-  |

| +3.3V       | 45     | 46    | Serial-RX1  |

| Serial-TX1  | 47     | 48    | Serial-CTS1 |

| Serial-RTS1 | 49     | 50    | SMBclk      |

| SMBalert#   | 51     | 52    | SMBdata     |

| Slot ID 2   | 53     | 54    | Slot ID 1   |

| Slot ID 0   | 55     | 56    | Present-    |

| JTAG-TDI    | 57     | 58    | JTAG-TDO    |

| JTAG-CLK    | 59     | 60    | JTAG-TMS    |

| Sys-Reset-  | 61     | 62    | Reserved    |

| +3.3V       | 63     | 64    | Ground      |

| +3.3V       | 65     | 66    | Ground      |

| Reserved    | 67     | 68    | Reserved    |

| Reserved    | 69     | 70    | Reserved    |

| +3.3V       | 71     | 72    | Ground      |

| Reserved    | 73     | 74    | Reserved    |

| Reserved    | 75     | 76    | Reserved    |

| +3.3V       | 77     | 78    | Ground      |

| Reserved    | 79     | 80    | Reserved    |

| Reserved    | 81     | 82    | Reserved    |

| Reserved    | 83     | 84    | Reserved    |

| Reserved    | 85     | 86    | Reserved    |

| +5V         | 87     | 88    | Ground      |

| +5V         | 89     | 90    | Ground      |

| I/OB-50     | 91     | 92    | I/OB-49     |

| I/OB-48     | 93     | 94    | I/OB-47     |

| I/OB-46     | 95     | 96    | I/OB-45     |

| I/OB-44     | 97     | 98    | I/OB-43     |

| I/OB-42     | 99     | 100   | I/OB-41     |

| I/OB-40     | 101    | 102   | I/OB-39     |

| I/OB-38     | 103    | 104   | I/OB-37     |

| I/OB-36     | 105    | 106   | I/OB-35     |

| I/OB-34     | 107    | 108   | I/OB-33     |

| I/OB-32     | 109    | 110   | I/OB-31     |

| I/OB-30     | 111    | 112   | I/OB-29     |

| I/OB-28     | 113    | 114   | I/OB-27     |

| ., 00 20    |        |       |             |

|                | Pin 11 | 5 – 230 |                    |

|----------------|--------|---------|--------------------|

| I/OB-26        | 115    | 116     | I/OB-25            |

| I/OB-24        | 117    | 118     | I/OB-23            |

| I/OB-22        | 119    | 120     | I/OB-21            |

| I/OB-20        | 121    | 122     | I/OB-19            |

| I/OB-18        | 123    | 124     | I/OB-17            |

| I/OB-16        | 125    | 126     | I/OB-15            |

| I/OB-14        | 123    | 128     | I/OB-13            |

| I/OB-12        | 129    | 130     | I/OB-13            |

| I/OB-12        | 131    | 132     | I/OB-9             |

| I/OB-8         | 133    | 134     | I/OB-3             |

| I/OB-6         | 135    | 136     | I/OB-5             |

| I/OB-4         | 137    | 138     | I/OB-3             |

| I/OB-2         | 139    | 140     | I/OB-3             |

| +5V            | 141    | 142     | Ground             |

| +5V            | 143    | 142     | Ground             |

|                | 145    | 144     |                    |

| +5V<br>I/OA-50 |        |         | Ground             |

| I/OA-50        | 147    | 148     | I/OA-49            |

|                | 149    | 150     | I/OA-47            |

| I/OA-46        | 151    | 152     | I/OA-45<br>I/OA-43 |

| I/OA-44        | 153    | 154     |                    |

| I/OA-42        | 155    | 156     | I/OA-41            |

| I/OA-40        | 157    | 158     | I/OA-39            |

| I/OA-38        | 159    | 160     | I/OA-37            |

| I/OA-36        | 161    | 162     | I/OA-35            |

| (NC)           | 163    | 164     | (NC)               |

| I/OA-34        | 165    | 166     | I/OA-33            |

| (NC)           | 167    | 168     | (NC)               |

| I/OA-32        | 169    | 170     | I/OA-31            |

| (NC)           | 171    | 172     | (NC)               |

| I/OA-30        | 173    | 174     | I/OA-29            |

| (NC)           | 175    | 176     | (NC)               |

| I/OA-28        | 177    | 178     | I/OA-27            |

| (NC)           | 179    | 180     | (NC)               |

| I/OA-26        | 181    | 182     | I/OA-25            |

| (NC)           | 183    | 184     | (NC)               |

| I/OA-24        | 185    | 186     | I/OA-23            |

| (NC)           | 187    | 188     | (NC)               |

| I/OA-22        | 189    | 190     | I/OA-21            |

| (NC)           | 191    | 192     | (NC)               |

| I/OA-20        | 193    | 194     | I/OA-19            |

| (NC)           | 195    | 196     | (NC)               |

| I/OA-18        | 197    | 198     | I/OA-17            |

| (NC)           | 199    | 200     | (NC)               |

| I/OA-16        | 201    | 202     | I/OA-15            |

| (NC)           | 203    | 204     | (NC)               |

| I/OA-14        | 205    | 206     | I/OA-13            |

| (NC)           | 207    | 208     | (NC)               |

| I/OA-12        | 209    | 210     | I/OA-11            |

| (NC)           | 211    | 212     | (NC)               |

| I/OA-10        | 213    | 214     | I/OA-9             |

| (NC)           | 215    | 216     | (NC)               |

| I/OA-8         | 217    | 218     | I/OA-7             |

| (NC)           | 219    | 220     | (NC)               |

| I/OA-6         | 221    | 222     | I/OA-5             |

| (NC)           | 223    | 224     | (NC)               |

| I/OA-4         | 225    | 226     | Ì/OÁ-3             |

| (NC)           | 227    | 228     | (NC)               |

| I/OA-2         | 229    | 230     | Ì/OÁ-1             |

|                |        |         |                    |

### 3.3 Analog I/O Signals

The FP-DAQ1616 module's analog I/O signals are brought out on FeaturePak connector pins 147 through 230 as shown here. The FeaturePak standard defines a Primary Group of pins for I/O; the mapping of those pins to the FP-DAQ1616 pins is in the table below. The FeaturePak specification allocates (up to) 34 pins for use either in isolated analog signal pairs for increased noise immunity, or as separate lines.

| 230 | Vin 0/0+       | 1  | 2  | Vin 8/0-        | 229 |

|-----|----------------|----|----|-----------------|-----|

| 226 | Vin 1/1+       | 3  | 4  | Vin 9/1-        | 225 |

| 222 | Vin 2/2+       | 5  | 6  | Vin 10/2-       | 221 |

| 218 | Vin 3/3+       | 7  | 8  | Vin 11/3-       | 217 |

| 214 | Vin 4/4+       | 9  | 10 | Vin 12/4-       | 213 |

| 210 | Vin 5/5+       | 11 | 12 | Vin 13/5-       | 209 |

| 206 | Vin 6/6+       | 13 | 14 | Vin 14/6-       | 205 |

| 202 | Vin 7/7+       | 15 | 16 | Vin 15/7-       | 201 |

| 198 | Aground (Vin)  | 17 | 18 | Aground (Vin)   | 197 |

| 194 | Vout 0         | 19 | 20 | Vout 8          | 193 |

| 190 | Vout 1         | 21 | 22 | Vout 9          | 189 |

| 186 | Vout 2         | 23 | 24 | Vout 10         | 185 |

| 182 | Vout 3         | 25 | 26 | Vout 11         | 181 |

| 178 | Vout 4         | 27 | 28 | Vout 12         | 177 |

| 174 | Vout 5         | 29 | 30 | Vout 13         | 173 |

| 170 | Vout 6         | 31 | 32 | Vout 14         | 169 |

| 166 | Vout 7         | 33 | 34 | Vout 15         | 165 |

| 162 | Aground (Vout) | 35 | 36 | Aground (Vout)  | 161 |

| 160 | ADTrig         | 37 | 38 | Ctr0Clk         | 159 |

| 158 | Ctr1Clk        | 39 | 40 | Ctr1Out         | 157 |

| 156 | Aux0           | 41 | 42 | Aux1            | 155 |

| 154 | Aux2           | 43 | 44 | Aux3            | 153 |

| 152 | ADGate / Aux4  | 45 | 46 | Aux5 / Ctr1Gate | 151 |

| 150 | WDTOut / Aux6  | 47 | 48 | Aux7 / WDTIn    | 149 |

| 148 | +3.3V          | 49 | 50 | Dground         | 147 |

| FeaturePak connector pin no. | Typical I/O connector pin no. | FeaturePak connector pin no. |

|------------------------------|-------------------------------|------------------------------|

|------------------------------|-------------------------------|------------------------------|

| Signal Name     Definition       Vin 7/7+ ~ Vin 0/0+     Analog input channels 7 – 0 in single-ended mode;<br>High side of input channels 7 – 0 in differential mode |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High side of input channels 7 – 0 in differential mode                                                                                                               |

|                                                                                                                                                                      |

| Vin 15/7- ~ Vin 8/0-Analog input channels 15 – 8 in both single-ended mode;<br>Low side of input channels 7 – 0 in differential mode                                 |

| Vout 0-15 Analog output channels 0 – 15                                                                                                                              |

| Aground (Vout), (Vin) Analog ground; used for analog signals only<br>Vout pin is for the analog outputs; Vin pin is for the analog inputs                            |

| Dground Digital ground reference for digital input signals                                                                                                           |

| AD Gate Enables A/D sampling when high or open, disables when pulled low                                                                                             |

| AD Trig External A/D trigger or clock input                                                                                                                          |

| Ctr0Clk, Ctr1Clk Counter 0/1 optional external clock inputs                                                                                                          |

| Ctr1Out Counter 1 output signal                                                                                                                                      |

| AUX0-7 Auxiliary digital I/O port; bit direction programmable; Line 4-7 have auxi functions for A/D gating, counter gating, and watchdog timer.                      |

### 3.4 Digital I/O Signals

The FP-DAQ1616's digital I/O signals are brought out on FeaturePak connector pins 91 through 140, as shown below.

#### FeaturePak connector pin no.

Typical I/O connector pin no. FeaturePak connector pin no.

| DIO A0          | 1                                                                                                                                                                                                                                                                                                                      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIO A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIO A2          | 3                                                                                                                                                                                                                                                                                                                      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIO A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO A4          | 5                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIO A5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO A6          | 7                                                                                                                                                                                                                                                                                                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIO A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO B0          | 9                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO B2          | 11                                                                                                                                                                                                                                                                                                                     | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO B3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO B4          | 13                                                                                                                                                                                                                                                                                                                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO B5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO B6          | 15                                                                                                                                                                                                                                                                                                                     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO B7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO C0          | 17                                                                                                                                                                                                                                                                                                                     | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO C2          | 19                                                                                                                                                                                                                                                                                                                     | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO C3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO C4          | 21                                                                                                                                                                                                                                                                                                                     | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO C5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO C6          | 23                                                                                                                                                                                                                                                                                                                     | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO C7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIO D0          | 25                                                                                                                                                                                                                                                                                                                     | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

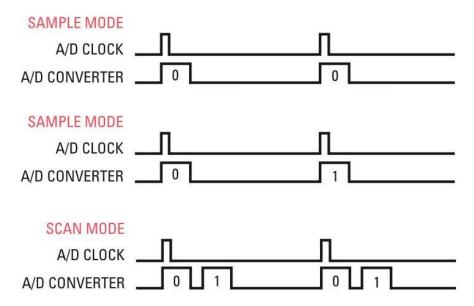

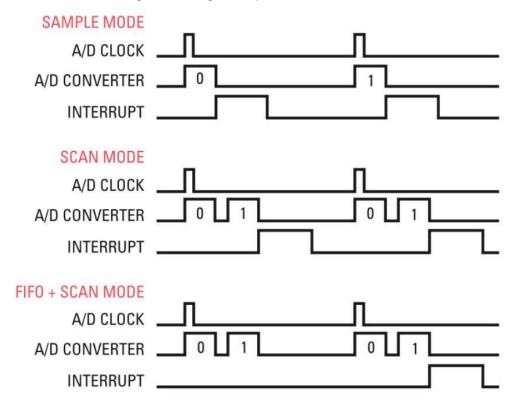

| DIO D2          | 27                                                                                                                                                                                                                                                                                                                     | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIO D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |